Integrated Octal 10/100/1000 Mbps Energy Efficient Ethernet Transceiver

Datasheet - Public

Doc. No. TD-000923 Rev. 1 October 5, 2020 Document Classification: Public

THIS DOCUMENT AND THE INFORMATION FURNISHED IN THIS DOCUMENT ARE PROVIDED "AS IS" WITHOUT ANY WARRANTY. MARVELL AND ITS AFFILIATES EXPRESSLY DISCLAIM AND MAKE NO WARRANTIES OR GUARANTEES, WHETHER EXPRESS, ORAL, IMPLIED, STATUTORY, ARISING BY OPERATION OF LAW, OR AS A RESULT OF USAGE OF TRADE, COURSE OF DEALING, OR COURSE OF PERFORMANCE, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NON-INFRINGEMENT.

This document, including any software or firmware referenced in this document, is owned by Marvell or Marvell's licensors, and is protected by intellectual property laws. No license, express or implied, to any Marvell intellectual property rights is granted by this document. The information furnished in this document is provided for reference purposes only for use with Marvell products. It is the user's own responsibility to design or build products with this information. Marvell products are not authorized for use as critical components in medical devices, military systems, life or critical support devices, or related systems. Marvell is not liable, in whole or in part, and the user will indemnify and hold Marvell harmless for any claim, damage, or other liability related to any such use of Marvell products.

Marvell assumes no responsibility for the consequences of use of such information or for any infringement of patents or other rights of third parties that may result from its use. You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning the Marvell products disclosed herein. Marvell and the Marvell logo are registered trademarks of Marvell or its affiliates. Please visit www.marvell.com for a complete list of Marvell trademarks and guidelines for use of such trademarks. Other names and brands may be claimed as the property of others.

Copyright © 2020. Marvell and/or its affiliates. All rights reserved.

### Alaska 88E1780 Integrated Octal 10/100/1000 Mbps Energy Efficient Ethernet Transceiver Datasheet - Public

# **1** Signal Description

# 1.1 Pin Description

#### Table 1: Pin Type Definitions

| Pin Type | Definition            |

|----------|-----------------------|

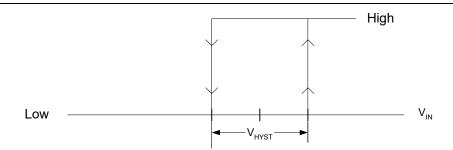

| н        | Input with hysteresis |

| I/O      | Input and output      |

| 1        | Input only            |

| 0        | Output only           |

| PU       | Internal pull-up      |

| PD       | Internal pull-down    |

| D        | Open drain output     |

| Z        | Tri-state output      |

| mA       | DC sink capability    |

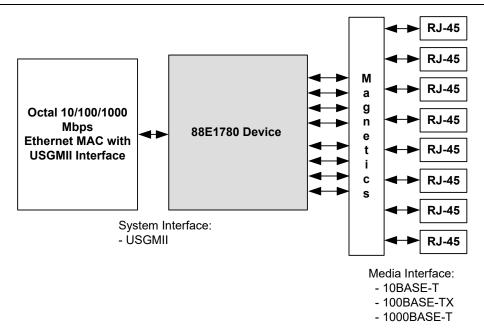

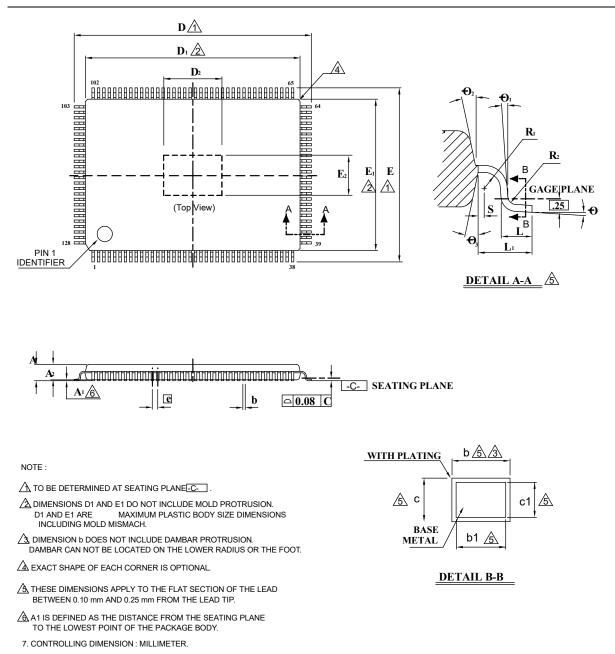

# 1.1.1 88E1780 128-Pin LQFP Package Pinout

#### Figure 2: 88E1780 Device 128-Pin LQFP Package with EPAD (Top View)

| 88E1780 Pin # | Pin Name                 | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|--------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 72<br>73      | P0_MDIP[0]<br>P0_MDIN[0] | I/O         | Media Dependent Interface[0].<br>In 1000BASE-T mode in MDI configuration, MDIP/N[0] correspond<br>to BI_DA±.<br>In MDIX configuration, MDIP/N[0] correspond to BI_DB±.<br>In 100BASE-TX and 10BASE-T modes in MDI configuration,<br>MDIP/N[0] are used for the transmit pair. In MDIX configuration,<br>MDIP/N[0] are used for the receive pair.<br><b>NOTE:</b> Unused MDI pins must be left floating.<br>The device contains an internal 100 ohm resistor between the<br>MDIP/N[0] pins. |

| 74<br>75      | P0_MDIP[1]<br>P0_MDIN[1] | I/O         | Media Dependent Interface[1].<br>In 1000BASE-T mode in MDI configuration, MDIP/N[1] correspond<br>to BI_DB±. In MDIX configuration, MDIP/N[1] correspond to<br>BI_DA±.<br>In 100BASE-TX and 10BASE-T modes in MDI configuration,<br>MDIP/N[1] are used for the receive pair. In MDIX configuration,<br>MDIP/N[1] are used for the transmit pair.<br>NOTE: Unused MDI pins must be left floating.<br>The device contains an internal 100 ohm resistor between the<br>MDIP/N[1] pins.        |

| 76<br>77      | P0_MDIP[2]<br>P0_MDIN[2] | I/O         | Media Dependent Interface[2].<br>In 1000BASE-T mode in MDI configuration, MDIP/N[2] correspond<br>to BI_DC±. In MDIX configuration, MDIP/N[2] correspond to<br>BI_DD±.<br>In 100BASE-TX and 10BASE-T modes, MDIP/N[2] are not used.<br><b>NOTE:</b> Unused MDI pins must be left floating.<br>The device contains an internal 100 ohm resistor between the<br>MDIP/N[2] pins.                                                                                                              |

| 78<br>79      | P0_MDIP[3]<br>P0_MDIN[3] | I/O         | Media Dependent Interface[3].<br>In 1000BASE-T mode in MDI configuration, MDIP/N[3] correspond<br>to BI_DD±. In MDIX configuration, MDIP/N[3] correspond to<br>BI_DC±.<br>In 100BASE-TX and 10BASE-T modes, MDIP/N[3] are not used.<br><b>NOTE:</b> Unused MDI pins must be left floating.<br>The device contains an internal 100 ohm resistor between the<br>MDIP/N[3] pins.                                                                                                              |

#### Table 2: Media Dependent Interface Port 0

| 88E1780 Pin # | Pin Name   | Pin<br>Type | Description                              |

|---------------|------------|-------------|------------------------------------------|

| 88            | P1_MDIP[0] | I/O         | Media Dependent Interface[0] for Port 1. |

| 87            | P1_MDIN[0] |             | Refer to P0_MDI[0]P/N.                   |

| 86            | P1_MDIP[1] | I/O         | Media Dependent Interface[1] for Port 1. |

| 85            | P1_MDIN[1] |             | Refer to P0_MDI[1]P/N.                   |

| 84            | P1_MDIP[2] | I/O         | Media Dependent Interface[2] for Port 1. |

| 83            | P1_MDIN[2] |             | Refer to P0_MDI[2]P/N.                   |

| 82            | P1_MDIP[3] | I/O         | Media Dependent Interface[3] for Port 1. |

| 81            | P1_MDIN[3] |             | Refer to P0_MDI[3]P/N.                   |

Table 3:

Media Dependent Interface Port 1

Table 4:

Media Dependent Interface Port 2

| 88E1780 Pin # | Pin Name   | Pin<br>Type | Description                              |

|---------------|------------|-------------|------------------------------------------|

| 89            | P2_MDIP[0] | I/O         | Media Dependent Interface[0] for Port 2. |

| 90            | P2_MDIN[0] |             | Refer to P0_MDI[0]P/N.                   |

| 91            | P2_MDIP[1] | I/O         | Media Dependent Interface[1] for Port 2. |

| 92            | P2_MDIN[1] |             | Refer to P0_MDI[1]P/N.                   |

| 93            | P2_MDIP[2] | I/O         | Media Dependent Interface[2] for Port 2. |

| 94            | P2_MDIN[2] |             | Refer to P0_MDI[2]P/N.                   |

| 95            | P2_MDIP[3] | I/O         | Media Dependent Interface[3] for Port 2. |

| 96            | P2_MDIN[3] |             | Refer to P0_MDI[3]P/N.                   |

Table 5:

Media Dependent Interface Port 3

| 88E1780 Pin # | Pin Name   | Pin<br>Type | Description                              |

|---------------|------------|-------------|------------------------------------------|

| 106           | P3_MDIP[0] | I/O         | Media Dependent Interface[0] for Port 3. |

| 105           | P3_MDIN[0] |             | Refer to P0_MDI[0]P/N.                   |

| 104           | P3_MDIP[1] | I/O         | Media Dependent Interface[1] for Port 3. |

| 103           | P3_MDIN[1] |             | Refer to P0_MDI[1]P/N.                   |

| 101           | P3_MDIP[2] | I/O         | Media Dependent Interface[2] for Port 3. |

| 100           | P3_MDIN[2] |             | Refer to P0_MDI[2]P/N.                   |

| 99            | P3_MDIP[3] | I/O         | Media Dependent Interface[3] for Port 3. |

| 98            | P3_MDIN[3] |             | Refer to P0_MDI[3]P/N.                   |

| 88E1780 Pin # | Pin Name   | Pin<br>Type | Description                              |

|---------------|------------|-------------|------------------------------------------|

| 4             | P4_MDIP[0] | I/O         | Media Dependent Interface[0] for Port 4. |

| 5             | P4_MDIN[0] |             | Refer to P0_MDI[0]P/N.                   |

| 6             | P4_MDIP[1] | I/O         | Media Dependent Interface[1] for Port 4. |

| 7             | P4_MDIN[1] |             | Refer to P0_MDI[1]P/N.                   |

| 8             | P4_MDIP[2] | I/O         | Media Dependent Interface[2] for Port 4. |

| 9             | P4_MDIN[2] |             | Refer to P0_MDI[2]P/N.                   |

| 10            | P4_MDIP[3] | I/O         | Media Dependent Interface[3] for Port 4. |

| 11            | P4_MDIN[3] |             | Refer to P0_MDI[3]P/N.                   |

Table 6:

Media Dependent Interface Port 4

Table 7:

Media Dependent Interface Port 5

| 88E1780 Pin # | Pin Name   | Pin<br>Type | Description                              |

|---------------|------------|-------------|------------------------------------------|

| 20            | P5_MDIP[0] | I/O         | Media Dependent Interface[0] for Port 5. |

| 19            | P5_MDIN[0] |             | Refer to P0_MDI[0]P/N.                   |

| 18            | P5_MDIP[1] | I/O         | Media Dependent Interface[1] for Port 5. |

| 17            | P5_MDIN[1] |             | Refer to P0_MDI[1]P/N.                   |

| 16            | P5_MDIP[2] | I/O         | Media Dependent Interface[2] for Port 5. |

| 15            | P5_MDIN[2] |             | Refer to P0_MDI[2]P/N.                   |

| 14            | P5_MDIP[3] | I/O         | Media Dependent Interface[3] for Port 5. |

| 13            | P5_MDIN[3] |             | Refer to P0_MDI[3]P/N.                   |

Table 8:

Media Dependent Interface Port 6

| 88E1780 Pin # | Pin Name   | Pin<br>Type | Description                              |

|---------------|------------|-------------|------------------------------------------|

| 21            | P6_MDIP[0] | I/O         | Media Dependent Interface[0] for Port 6. |

| 22            | P6_MDIN[0] |             | Refer to P0_MDI[0]P/N.                   |

| 23            | P6_MDIP[1] | I/O         | Media Dependent Interface[1] for Port 6. |

| 24            | P6_MDIN[1] |             | Refer to P0_MDI[1]P/N.                   |

| 25            | P6_MDIP[2] | I/O         | Media Dependent Interface[2] for Port 6. |

| 26            | P6_MDIN[2] |             | Refer to P0_MDI[2]P/N.                   |

| 27            | P6_MDIP[3] | I/O         | Media Dependent Interface[3] for Port 6. |

| 28            | P6_MDIN[3] |             | Refer to P0_MDI[3]P/N.                   |

| 88E1780 Pin # | Pin Name   | Pin<br>Type | Description                              |

|---------------|------------|-------------|------------------------------------------|

| 37            | P7_MDIP[0] | I/O         | Media Dependent Interface[0] for Port 7. |

| 36            | P7_MDIN[0] |             | Refer to P0_MDI[0]P/N.                   |

| 35            | P7_MDIP[1] | I/O         | Media Dependent Interface[1] for Port 7. |

| 34            | P7_MDIN[1] |             | Refer to P0_MDI[1]P/N.                   |

| 33            | P7_MDIP[2] | I/O         | Media Dependent Interface[2] for Port 7. |

| 32            | P7_MDIN[2] |             | Refer to P0_MDI[2]P/N.                   |

| 31            | P7_MDIP[3] | I/O         | Media Dependent Interface[3] for Port 7. |

| 30            | P7_MDIN[3] |             | Refer to P0_MDI[3]P/N.                   |

Table 9:

Media Dependent Interface Port 7

Table 10: USGMII Interface

| 88E1780 Pin # | Pin Name         | Pin<br>Type | Description                                                                                                                                                                                                                                                 |

|---------------|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 46<br>48      | U_INP<br>U_INN   | 1           | USGMII Transmit Data. 10 GBaud input - Positive and Negative.<br>AC Coupling connection must be used for the USGMII interface.<br>0.1uF is recommended for each of the USGMII signals. DC<br>Coupling connection is not supported for the USGMII interface. |

| 56<br>54      | U_OUTP<br>U_OUTN | 0           | USGMII Receive Data. 10 GBaud output - Positive and Negative.<br>AC Coupling connection must be used for the USGMII interface.<br>0.1uF is recommended for each of the USGMII signals. DC<br>Coupling connection is not supported for the USGMII interface. |

Table 11: Synchronous Ethernet Interface/PTP

| 88E1780 Pin # | Pin Name    | Pin<br>Type | Description                        |

|---------------|-------------|-------------|------------------------------------|

| 115           | RCLK1       | 0           | First 25/125 MHz Recovered Clock.  |

| 117           | RCLK2       | 0           | Second 25/125 MHz Recovered Clock. |

| 64            | PTP_TRIG_IN | I           | PTP event request input.           |

| 88E1780 Pin # | Pin Name | Pin<br>Type | Description                                                                                                                                                                                                        |

|---------------|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63            | MDC      | 1           | Management Clock pin.<br>MDC is the management data clock reference for the serial<br>management interface. A continuous clock stream is not expected.<br>The maximum frequency supported is 25 MHz.               |

| 62            | MDIO     | I/O         | Management Data pin.<br>MDIO is the management data. MDIO transfers management data<br>in and out of the device synchronously to MDC. This pin requires a<br>pull-up resistor in a range from 1.5 kohm to 10 kohm. |

| 61            | INTn     | OD          | Interrupt pin. INTn functions as an active low interrupt output. This pin requires a pull-up resister. The pull-up resistor used for the INTn pin should not be connected to voltage higher than VDDOR.            |

#### Table 12: Management Interface/Control

#### Table 13: LED/Configuration

| 88E1780 Pin #                                        | Pin Name                                                                     | Pin<br>Type | Description                                                                        |

|------------------------------------------------------|------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------|

| 110<br>111<br>112<br>113<br>121<br>122<br>124<br>125 | P0_LED<br>P1_LED<br>P2_LED<br>P3_LED<br>P4_LED<br>P5_LED<br>P6_LED<br>P7_LED | 0           | Parallel LED Output Port 0 to Port 7.<br>Matrix LED Input/Output Port 0 to Port 7. |

| 118                                                  | CONFIG[0]                                                                    | I           | Global hardware configuration.                                                     |

| 119                                                  | CONFIG[1]                                                                    | I           | See Section 2.3.1, Hardware Configuration, on page 24 for details.                 |

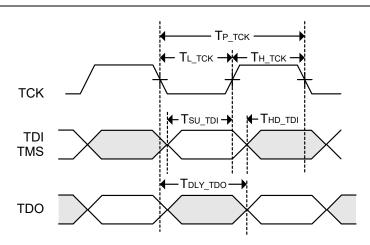

#### Table 14: JTAG

| 88E1780 Pin # | Pin Name | Pin<br>Type | Description                                                                                                                                                                                     |

|---------------|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | TDI      | I, PU       | Boundary scan test data input. TDI contains an internal 150 kohm pull-up resistor.                                                                                                              |

| 2             | TMS      | I, PU       | Boundary scan test mode select input. TMS contains an internal 150 kohm pull-up resistor.                                                                                                       |

| 128           | ТСК      | I, PU       | Boundary scan test clock input. TCK contains an internal 150 kohm pull-up resistor.                                                                                                             |

| 126           | TRSTn    | I, PU       | Boundary scan test reset input. Active low.<br>TRSTn contains an internal 150 kohm pull-up resistor. For normal<br>operation, TRSTn should be pulled low with a 4.7 kohm pull-down<br>resistor. |

| 127           | TDO      | 0           | Boundary scan test data output.                                                                                                                                                                 |

| 88E1780 Pin # | Pin Name                 | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|--------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

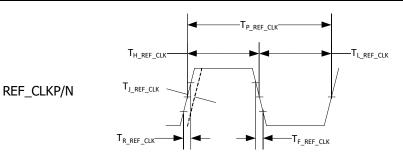

| 70            | REF_CLKP                 | I           | 125 MHz/156.25 MHz Reference Clock Input Positive and Negative +/- 50 ppm tolerance differential clock inputs.                                                                                                                                                                                                                                                                                                                                           |

| 69            | REF_CLKN                 |             | The inputs are LVDS differential inputs with a 100 ohm differential internal termination resistor and internal ac-coupling. REF_CLKP/N also supports 125 MHz single-ended clock. In this case, the unused pin must be connected with 0.1uF capacitor to ground.<br>The reference clock input voltage level should not be higher than AVDD15.<br>The following REF_CLK inputs are supported:<br>• 156.25 MHz LVDS REF_CLKP/N<br>• 125 MHz LVDS REF_CLKP/N |

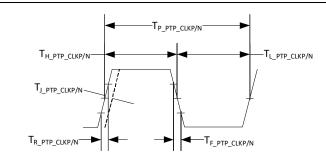

| 67            | PTP_CLKP                 | I           | PCH time stamp clock.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 66            | PTP_CLKN                 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 108<br>107    | CLK_SEL[1]<br>CLK_SEL[0] | 1           | Reference Clock Selection<br>CLK_SEL[1:0]<br>00 = Use 156.25 MHz REF_CLKP/N<br>01 = Use 125 MHz REF_CLKP/N<br>10 = Reserved<br>11 = Reserved<br>CLK_SEL[1:0] must be connected to VDDOL for configuration<br>HIGH.                                                                                                                                                                                                                                       |

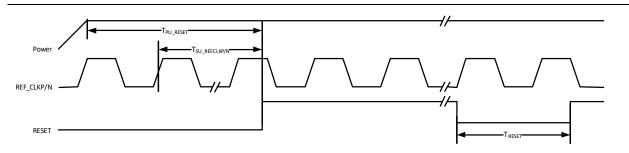

| 60            | RESETn                   | 1           | Hardware reset. The reference clock must be active for a minimum of 10 clock cycles before the rising edge of RESETn. RESETn must                                                                                                                                                                                                                                                                                                                        |

|               |                          |             | be in inactive state for normal operation.<br>1 = Normal operation<br>0 = Reset                                                                                                                                                                                                                                                                                                                                                                          |

#### Table 16: Test

| 88E1780 Pin # | Pin Name         | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                    |

|---------------|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40<br>39      | HSDACP<br>HSDACN | 0           | AC Test Points (Positive and Negative), TX_TCLK.<br>The HSDACP/N outputs are used for AC Test Points and<br>TX_TCLK. These pins must be connected to a 50 ohm<br>termination resistor to VSS. These pins can be left<br>floating if not used for IEEE testing,<br>and debug test points are not of importance. |

| 43            | TSTPT            | 0           | Pin should be left floating.                                                                                                                                                                                                                                                                                   |

| 120           | TEST0            | I           | Tie to ground with a 4.7 kohm resistor.                                                                                                                                                                                                                                                                        |

#### Table 17: Reference

| 88E1780 Pin # | Pin Name | Pin<br>Type | Description                                                              |

|---------------|----------|-------------|--------------------------------------------------------------------------|

| 42            | RSET     | I           | Resistor Reference<br>External 5.0 kohm 1% resistor connected to ground. |

#### Table 18: Power & Ground

| 88E1780 Pin #                                      | Pin Name | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 59<br>114<br>116                                   | DVDD     | Power       | 1.15V Digital Supply                                                                                                                                                                                                                                                                                                                                                                    |

| 3<br>38<br>41<br>50<br>51<br>52<br>68<br>71<br>102 | AVDD15   | Power       | 1.5V Analog Supply <sup>1</sup> .                                                                                                                                                                                                                                                                                                                                                       |

| 12<br>29<br>80<br>97                               | AVDD33   | Power       | 3.3V Analog Supply.                                                                                                                                                                                                                                                                                                                                                                     |

| 109<br>123                                         | VDDOL    | Power       | <ul> <li>2.5V or 3.3V I/O Supply<sup>2</sup>.</li> <li>NOTE: The I/O voltage supplied by VDDOL is not tolerant to any other voltage levels.</li> </ul>                                                                                                                                                                                                                                  |

| 65                                                 | VDDOR    | Power       | 1.8V, 2.5V, or 3.3V I/O Supply <sup>3</sup> . The I/O supplied by the VDDOR is not tolerant to any other voltage levels.                                                                                                                                                                                                                                                                |

| 44<br>45<br>49<br>53<br>57<br>58                   | AVSS     | Ground      | Ground.                                                                                                                                                                                                                                                                                                                                                                                 |

| EPAD                                               | VSS      | Ground      | Ground to device. The device is packaged in a 128-pin LQFP package with an EPAD (exposed die pad) on the bottom of the package. This EPAD must be soldered to VSS as it is the main VSS connection on the device.<br>The location and dimensions of the EPAD can be found in Table 53.<br>See the Marvell <sup>®</sup> EPAD Layout Guidelines Application Note for EPAD layout details. |

AVDD15 supplies analog core, REFCLKP, REFCLKN, TSTPT, PTP\_CLKP, PTP\_CLKN, RSET, HSDACP, and HSDACN.

VDDOL supplies digital I/O pins TDO, TDI, TMS, TCK, TRSTn, RCLK1, RCLK2, LED, CONFIG, and CLK\_SEL[1:0].

VDDOR supplies digital I/O pins PTP\_TRIG\_IN, RESETn, MDC, MDIO, and INTn.

#### Table 19: Do Not Connect

| Pin # | Pin Name | Pin Type   | Description                                          |

|-------|----------|------------|------------------------------------------------------|

| 47    | DNC0     | No Connect | Do not connect. Do not connect this pin to anything. |

| 55    | DNC1     |            |                                                      |

#### Table 20: I/O State at Various Test or Reset Modes

| Pin(s)      | Loopback | Software Reset                                     | Hardware Reset                                  | Power Down                                                                                                                  |

|-------------|----------|----------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| MDI[3:0]P/N | Active   | Tri-state                                          | Tri-state                                       | Tri-state                                                                                                                   |

| U_OUTP/N    | Active   | Internally pulled up by<br>terminations of 50 ohms | Internally pulled up by terminations of 50 ohms | Reg. 0_30.11 (Page 30, Register<br>0, bit 11) state<br>0 = Internally pulled up by<br>terminations of 50 ohms<br>1 = Active |

| MDIO        | Active   | Active                                             | Tri-state                                       | Active                                                                                                                      |

| INTn        | Active   | Tri-state                                          | Tri-state                                       | Tri-state                                                                                                                   |

| TDO         | Active   | Active                                             | Active                                          | Active                                                                                                                      |

MARVELL Alaska 88E1780 Datasheet - Public

# 1.2 Pin Assignment List

# 1.2.1 88E1780 128-Pin LQFP Package Pin Assignment List

Table 21: 88E1780 128-Pin LQFP List—Alphabetical by Signal Name

| Pin Name   | Pin Number |

|------------|------------|

| AVDD15     | 3          |

| AVDD15     | 38         |

| AVDD15     | 41         |

| AVDD15     | 50         |

| AVDD15     | 51         |

| AVDD15     | 52         |

| AVDD15     | 68         |

| AVDD15     | 71         |

| AVDD15     | 102        |

| AVDD33     | 12         |

| AVDD33     | 29         |

| AVDD33     | 80         |

| AVDD33     | 97         |

| AVSS       | 44         |

| AVSS       | 45         |

| AVSS       | 49         |

| AVSS       | 53         |

| AVSS       | 57         |

| AVSS       | 58         |

| CLK_SEL[0] | 107        |

| CLK_SEL[1] | 108        |

| CONFIG[0]  | 118        |

| CONFIG[1]  | 119        |

| DNC0       | 47         |

| DNC1       | 55         |

| Pin Name   | Pin Number |

|------------|------------|

| DVDD       | 59         |

| DVDD       | 114        |

| DVDD       | 116        |

| HSDACN     | 39         |

| HSDACP     | 40         |

| INTn       | 61         |

| MDC        | 63         |

| MDIO       | 62         |

| P0_LED[0]  | 110        |

| P0_MDIN[0] | 73         |

| P0_MDIN[1] | 75         |

| P0_MDIN[2] | 77         |

| P0_MDIN[3] | 79         |

| P0_MDIP[0] | 72         |

| P0_MDIP[1] | 74         |

| P0_MDIP[2] | 76         |

| P0_MDIP[3] | 78         |

| P1_LED[0]  | 111        |

| P1_MDIN[0] | 87         |

| P1_MDIN[1] | 85         |

| P1_MDIN[2] | 83         |

| P1_MDIN[3] | 81         |

| P1_MDIP[0] | 88         |

| P1_MDIP[1] | 86         |

| P1_MDIP[2] | 84         |

| Pin Name   | Pin Number |

|------------|------------|

| P1_MDIP[3] | 82         |

| P2_LED[0]  | 112        |

| P2_MDIN[0] | 90         |

| P2_MDIN[1] | 92         |

| P2_MDIN[2] | 94         |

| P2_MDIN[3] | 96         |

| P2_MDIP[0] | 89         |

| P2_MDIP[1] | 91         |

| P2_MDIP[2] | 93         |

| P2_MDIP[3] | 95         |

| P3_LED[0]  | 113        |

| P3_MDIN[0] | 105        |

| P3_MDIN[1] | 103        |

| P3_MDIN[2] | 100        |

| P3_MDIN[3] | 98         |

| P3_MDIP[0] | 106        |

| P3_MDIP[1] | 104        |

| P3_MDIP[2] | 101        |

| P3_MDIP[3] | 99         |

| P4_LED[0]  | 121        |

| P4_MDIN[0] | 5          |

| P4_MDIN[1] | 7          |

| P4_MDIN[2] | 9          |

| P4_MDIN[3] | 11         |

| P4_MDIP[0] | 4          |

| P4_MDIP[1] | 6          |

| P4_MDIP[2] | 8          |

| P4_MDIP[3] | 10         |

| Pin Name   | Pin Number |

|------------|------------|

| P5_LED[0]  | 122        |

| P5_MDIN[0] | 19         |

| P5_MDIN[1] | 17         |

| P5_MDIN[2] | 15         |

| P5_MDIN[3] | 13         |

| P5_MDIP[0] | 20         |

| P5_MDIP[1] | 18         |

| P5_MDIP[2] | 16         |

| P5_MDIP[3] | 14         |

| P6_LED[0]  | 124        |

| P6_MDIN[0] | 22         |

| P6_MDIN[1] | 24         |

| P6_MDIN[2] | 26         |

| P6_MDIN[3] | 28         |

| P6_MDIP[0] | 21         |

| P6_MDIP[1] | 23         |

| P6_MDIP[2] | 25         |

| P6_MDIP[3] | 27         |

| P7_LED[0]  | 125        |

| P7_MDIN[0] | 36         |

| P7_MDIN[1] | 34         |

| P7_MDIN[2] | 32         |

| P7_MDIN[3] | 30         |

| P7_MDIP[0] | 37         |

| P7_MDIP[1] | 35         |

| P7_MDIP[2] | 33         |

| P7_MDIP[3] | 31         |

| PTP_CLKN   | 66         |

| Pin Name    | Pin Number |  |  |  |

|-------------|------------|--|--|--|

| PTP_CLKP    | 67         |  |  |  |

| PTP_TRIG_IN | 64         |  |  |  |

| RCLK1       | 115        |  |  |  |

| RCLK2       | 117        |  |  |  |

| REF_CLKN    | 69         |  |  |  |

| REF_CLKP    | 70         |  |  |  |

| RESETn      | 60         |  |  |  |

| RSET        | 42         |  |  |  |

| тск         | 128        |  |  |  |

| TDI         | 1          |  |  |  |

| TDO         | 127        |  |  |  |

| TEST0       | 120        |  |  |  |

| Pin Name | Pin Number |  |  |

|----------|------------|--|--|

| TMS      | 2          |  |  |

| TRSTn    | 126        |  |  |

| TSTPT    | 43         |  |  |

| U_INN    | 48         |  |  |

| U_INP    | 46<br>54   |  |  |

| U_OUTN   |            |  |  |

| U_OUTP   | 56         |  |  |

| VDDOL    | 109        |  |  |

| VDDOL    | 123        |  |  |

| VDDOR    | 65         |  |  |

| VSS      | EPAD       |  |  |

# **2** Functional Details

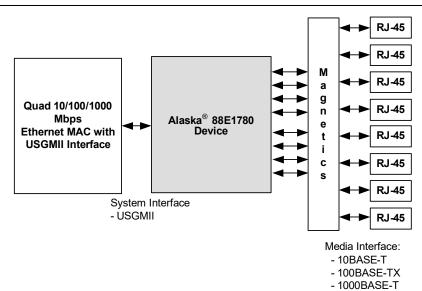

# Modes of Operation and Major Interfaces

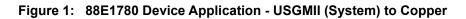

The device has two separate major electrical interfaces:

- MDI Interface to Copper Cable

- USGMII Interface

2.1

The MDI Interface is the media interface. The USGMII Interface is the system interface. (The system interface is also known as MAC interface. It is typically the connection between the PHY and the MAC or the system ASIC.) For example:

# 2.2 LED

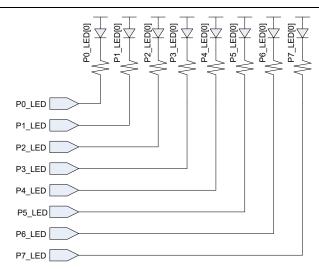

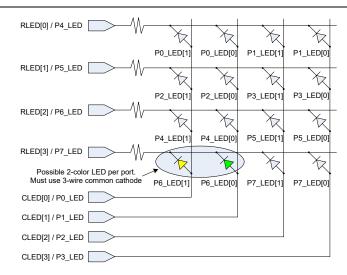

The device supports two modes of LED operation: one direct connect LED (LED[0]) per port OR two LEDs (LED[1:0]) per port in a 4x4 matrix configuration. The LEDs are programmable to indicate link, speed, and activity functions. The LEDs are by default configured to use Single LED Mode after hard-reset. To change the LED mode to Matrix LED Mode, write Reg 1\_28.10 = `1'.

The Px\_LED pins are used to drive LED pins. Registers 16\_3, 17\_3, 18\_3, and 19\_3 controls the operation of the LED pins. Px\_LED pins are also used to configure the PHY per Section 2.3.1, Hardware Configuration, on page 24. After the configuration is completed, Px\_LED pins will operate per this section.

Register 16\_3.7:4 controls the LED[1] function and register 16\_3.3:0 controls the LED[0] function. In a single LED mode, each of the Px\_LED pin corresponds to the port's LED[0]. In matrix LED mode, the Px\_LED are divided into rows and columns where the rows signal (RLED) connected to the anode of each LEDs and columns signal (CLED) connected to the cathode of each LEDs. Table 22 shows an example of implementation using matrix LED mode.

There are some LED modes where LED[1:0] operate as a unit. This is entered when register  $16_{-3.3:2}$  is set to 11, which is referred to as dual LED modes. In dual LED modes, register  $16_{-3.7:4}$  have no meaning when  $16_{-3.3:2}$  is set to 11.

The LED reports the status of the copper media interface.

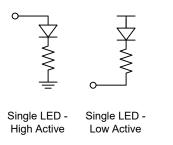

Figure 4 shows a Single LED mode example.

Figure 5 shows a Matrix LED mode example, and Table 22 shows LED mapping in Matrix LED mode.

#### Figure 4: Single LED Mode Example

#### Table 22: LED Mapping

|                               | CLED[0]/P0_LED                             | CLED[1]/P1_LED | CLED[2]/P2_LED | CLED[3]/P3_LED |  |

|-------------------------------|--------------------------------------------|----------------|----------------|----------------|--|

| RLED[0]/P4_LED Port 0, LED[1] |                                            | Port 0, LED[0] | Port 1, LED[1] | Port 1, LED[0] |  |

| RLED[1]/P5_LED                | Port 2, LED[1]                             | Port 2, LED[0] | Port 3, LED[1] | Port 3, LED[0] |  |

| RLED[2]/P6_LED                | ED[2]/P6_LED Port 4, LED[1] Port 4, LED[0] |                | Port 5, LED[1] | Port 5, LED[0] |  |

| RLED[3]/P7_LED                | LED[3]/P7_LED Port 6, LED[1]               |                | Port 7, LED[1] | Port 7, LED[0] |  |

#### Figure 5: Matrix LED Mode Example

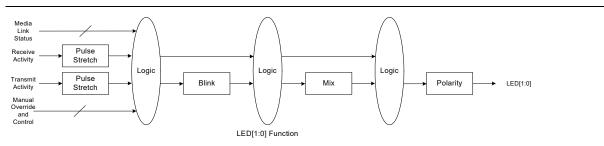

Figure 6 shows the general chaining of function for the LEDs. The various functions are described in the following sections.

Figure 6: LED Chain

## 2.2.1 LED Polarity

There are two ways to hook up the LED in single LED mode as shown in Figure 4. In the matrix LED mode, the LEDs must be connected as shown in Figure 5. In order to make things more flexible registers 17\_3.3:2, and 17\_3.1:0 specify the output polarity for the LED[1:0] function. The lower bit of each pair specified the on (active) state of the LED, either high or low. The upper bit of each pair specifies whether the off state of the LED should be driven to the opposite level of the on state or Hi-Z. The Hi-Z state is useful in cases such the LOS and INIT function where the inactive state is Hi-Z.

#### Figure 7: Single LED Mode Configurations

#### Table 23: LED Polarity

| Register | LED Function | Definition                                                                                                                                                                                                            |

|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17_3.3:2 | LED[1]       | 00 = On - drive LED[1] low, Off - drive LED[1] high<br>01 = On - drive LED[1] high, Off - drive LED[1] low<br>10 = On - drive LED[1] low, Off - tristate LED[1]<br>11 = On - drive LED[1] high, Off - tristate LED[1] |

| 17_3.1:0 | LED[0]       | 00 = On - drive LED[0] low, Off - drive LED[0] high<br>01 = On - drive LED[0] high, Off - drive LED[0] low<br>10 = On - drive LED[0] low, Off - tristate LED[0]<br>11 = On - drive LED[0] high, Off - tristate LED[0] |

# 2.2.2 Pulse Stretching and Blinking

Register 18\_3.14:12 specifies the pulse stretching duration of a particular activity. Only the transmit activity, receive activity, and (transmit or receive) activity are stretched. All other statuses are not stretched since they are static in nature and no stretching is required.

Some status will require blinking instead of a solid on. Register 18\_3.10:8 specifies the blink rate. Note that the pulse stretching is applied first and the blinking will reflect the duration of the stretched pulse.

The stretched/blinked output will then be mixed if needed (Section 2.2.3) and then inverted/Hi-Z according to the polarity described in section (Section 2.2.1)

Table 24:

Pulse Stretching and Blinking

| Register   | LED Function              | Definition                                                                                                                                                                                           |

|------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18_3.14:12 | Pulse stretch<br>duration | 000 = No pulse stretching<br>001 = 21 ms to 42 ms<br>010 = 42 ms to 84 ms<br>011 = 84 ms to 170 ms<br>100 = 170 ms to 340 ms<br>101 = 340 ms to 670 ms<br>110 = 670 ms to 1.3s<br>111 = 1.3s to 2.7s |

| 18_3.10:8  | Blink Rate                | 000 = 42 ms<br>001 = 84 ms<br>010 = 170 ms<br>011 = 340 ms<br>100 = 670 ms<br>101 to 111 = Reserved                                                                                                  |

# 2.2.3 Bi-Color LED Mixing

Bi-color LED mixing applies only when the LEDs are used in the matrix LED mode configuration. There is no mixing in the single LED mode. The bi-color LED mixing allows the two colors of the LED to be mixed to form a third color. This is useful since the PHY is tri speed and the three colors each represent one of the speeds. The LED color mixing can be done by controlling when the LED turned ON or OFF individually (by forcing the LED to be ON or OFF) or by enabling the dual LED mode. The dual LED mode mixing is enabled when register 16 3.3:0 are set to 11xx.

In dual LED mode, Register 17\_3.15:12 control the amount to mix in the LED[1] pin. Register 17\_3.11:8 control the amount to mix in the LED[0] pin. The mixing is determined by the percentage of time the LED is on during the active state. The percentage is selectable in 12.5% increments.

In this configuration, both of the LEDs can be turned on at the same time. Hence the sum of the percentage specified by  $17_3.15:12$  and  $17_3.11:8$  can exceed 100%.

| Register   | LED Function             | Definition                                                                           |

|------------|--------------------------|--------------------------------------------------------------------------------------|

| 17_3.15:12 | LED[1] mix<br>percentage | 0000 = 0%<br>0001 = 12.5%                                                            |

|            |                          | 0111 = 87.5%<br>1000 = 100%<br>1001 to 1111 = Reserved                               |

| 17_3.11:8  | LED[0] mix<br>percentage | 0000 = 0%<br>0001 = 12.5%,<br>0111 = 87.5%<br>1000 = 100%<br>1001 to 1111 = Reserved |

#### Table 25: Bi-Color LED Mixing

# 2.2.4 Modes of Operation

The LED pins relay some modes of the PHY so that these modes can be displayed by the LEDs.

| Register | LED Function   | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16_3.7:4 | LED[1] Control | If 16_3.3:2 is set to 11 then 16_3.7:4 has no effect<br>0000 = On - Copper Link, Off - Else<br>0001 = On - Link, Blink - Activity, Off - No Link<br>0010 = On - Link, Blink - Receive, Off - No Link<br>0011 = On - Activity, Off - No Activity<br>0100 = Blink - Activity, Off - No Activity<br>0101 = On - 100 Mbps, Link or Fiber Link, Off - Else<br>0110 = On - 100/1000 Mbps Link, Off - Else<br>0111 = On - 100 Mbps Link, Off - Else<br>1000 = Force Off<br>1001 = Force On<br>1010 = Force Hi-Z<br>1011 = Force Blink<br>11xx = Reserved                                                                              |

| 16_3.3:0 | LED[0] Control | 0000 = On - Link, Off - No Link<br>0001 = On - Link, Blink - Activity, Off - No Link<br>0010 = 3 blinks - 100 Mbps<br>2 blinks - 100 Mbps<br>1 blink - 10 Mbps<br>0 blink - No Link<br>0011 = On - Activity, Off - No Activity<br>0100 = Blink - Activity, Off - No Activity<br>0101 = On - Transmit, Off - No Transmit<br>0110 = On - Copper Link, Off - Else<br>0111 = On - 1000 Mbps Link, Off - Else<br>1000 = Force Off<br>1001 = Force On<br>1010 = Force Hi-Z<br>1011 = Force Blink<br>1100 = MODE 1 (Dual LED mode)<br>1101 = MODE 2 (Dual LED mode)<br>1111 = MODE 3 (Dual LED mode)<br>1111 = MODE 4 (Dual LED mode) |

Table 26:

Modes of Operation

# 2.3 Configuring the Device

The device can be configured two ways:

- Hardware configuration strap options (unmanaged applications)

- MDC/MDIO register writes (managed applications)

The hardware configuration options (PHYADR[4:2] and PHY\_ORDER) cannot be overwritten by software.

## 2.3.1 Hardware Configuration

After the deassertion of RESETn the device will be hardware configured.

The device is configured through the CONFIG pin and CLK\_SEL[1:0]. By default, the device is configured in power down mode with a single LEDs per port after deassertion of RESETn. If Matrix LEDs are used, the Matrix LEDs can be enabled through software configuration.

CLK\_SEL[1:0] are used to select the reference clock input option.

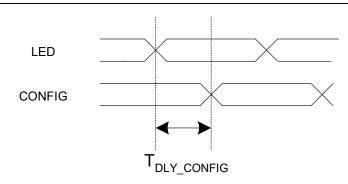

The CONFIG pin is used to configure 4 bits. The 4-bit value is set depending on what is connected to the CONFIG pin soon after the deassertion of hardware reset. The 4-bit mapping is shown in Table 27.

| Pin    | Bit[3:0] |  |

|--------|----------|--|

| VDDOL  | 1111     |  |

| P6_LED | 1110     |  |

| P5_LED | 1101     |  |

| P4_LED | 1100     |  |

| P3_LED | 1011     |  |

| P2_LED | 1010     |  |

| P1_LED | 1001     |  |

| VSS    | 0000     |  |

Table 27: Four Bit Mapping

The 4 bits for the CONFIG pin is mapped as shown in Table 28.

#### Table 28: Configuration Mapping

| Pin       | Pin Bit3 Bit 2           |           | Bit1      | Bit 0     |

|-----------|--------------------------|-----------|-----------|-----------|

| CONFIG[0] | Reserved. Set to 0 or 1. | PHY_ORDER | PHYADR[4] | PHYADR[3] |

| CONFIG[1] | Reserved. Set to 0 or 1. | LED_MODE  | PCH_EN    | PWRDN     |

Each bit in the configuration is defined as shown in Table 29.

Table 29:

Device Configuration Definition

| Bits       | Definition                                                                                                                                                                                                                                                                                                                                            | Register Affected |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| PHYAD[4:3] | Two MSB of the 5-bit PHY address                                                                                                                                                                                                                                                                                                                      | None              |

| PHY_ORDER  | $1 = PHYAD[2:0] \text{ is set as follows:} \\Port 7 = 000 \\Port 6 = 001 \\Port 5 = 010 \\Port 4 = 011 \\Port 3 = 100 \\Port 2 = 101 \\Port 1 = 110 \\Port 0 = 111 \\0 = PHYAD[2:0] \text{ is set as follows:} \\Port 0 = 000 \\Port 1 = 001 \\Port 2 = 010 \\Port 3 = 011 \\Port 4 = 100 \\Port 5 = 101 \\Port 6 = 110 \\Port 7 = 111 \end{aligned}$ | None              |

| PDOWN      | Power state of the PHY at power up:<br>1 = Power down<br>0 = Power up                                                                                                                                                                                                                                                                                 | 0.11, 16_0.2      |

| PCH_EN     | 0 = PCH is bypassed,<br>1 = PCH is not bypassed.<br>PCH_EN will be the default value of PCH's TBD register bit, which will<br>bypass the PCH logic. This TBD bit should be able to overwrite through<br>MDIO interface.                                                                                                                               | 28_14.10          |

| LED_MODE   | LED_MODE 1 = Normal led mode<br>0 = Matrix led mode                                                                                                                                                                                                                                                                                                   |                   |

ARVELL<sup>®</sup> Alaska 88E1780 Datasheet - Public

## 2.3.2 Software Configuration - Management Interface

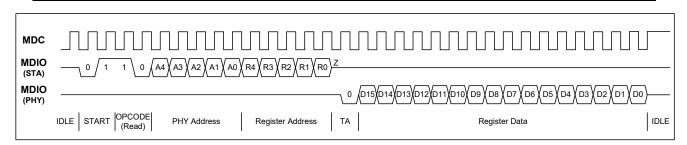

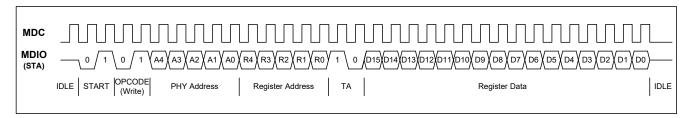

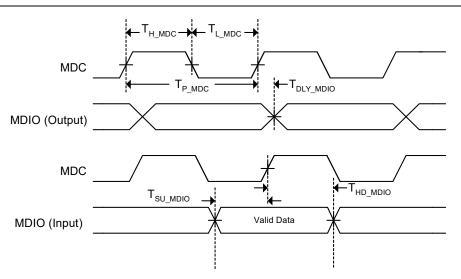

The management interface provides access to the internal registers via the MDC and MDIO pins and is compliant with IEEE 802.3 Clause 22 and Clause 45 MDIO protocol. MDC is the management data clock input and, it can run from DC to a maximum rate of 12.5 MHz. At high MDIO fanouts the maximum rate may be decreased depending on the output loading. MDIO is the management data input/output and is a bi-directional signal that runs synchronously to MDC.

The MDIO pin requires a pull-up resistor in a range from 1.5 kohm to 10 kohm that pulls the MDIO high during the idle and turnaround.

PHY address is configured during the hardware reset sequence. Refer to Section 2.3.1, Hardware Configuration, on page 24 for more information on how to configure PHY addresses.

All the required serial management registers are implemented as well as several optional registers. A description of the registers can be found in the Register Description.

#### 2.3.2.1 Clause 22 MDC/MDIO Management Interface

Typical read and write operations on the management interface are shown in Figure 8 and Figure 9.

#### Figure 8: Typical MDC/MDIO Read Operation

#### Figure 9: Typical MDC/MDIO Write Operation

#### Table 30 is an example of a read operation.

#### Table 30: Serial Management Interface Protocol

| 32-Bit<br>Preamble | Start of<br>Frame | OpCode<br>Read =<br>10<br>Write = 01 | 5-Bit<br>PHY<br>Device<br>Address | 5-Bit<br>PHY<br>Register<br>Address<br>(MSB) | 2-Bit<br>Turn<br>around<br>Read = z0<br>Write = 10 | 16-Bit<br>Data Field | ldle     |

|--------------------|-------------------|--------------------------------------|-----------------------------------|----------------------------------------------|----------------------------------------------------|----------------------|----------|

| 11111111           | 01                | 10                                   | 01100                             | 00000                                        | z0                                                 | 0001001100000000     | 11111111 |

### 2.3.2.2 Extended Register Access

The IEEE defines only 32 registers address space for the PHY. In order to extend the number of registers address space available a paging mechanism is used. Register 22 bits 7 to 0 are used to specify the page. There is no paging for registers 22.

In this document, the short hand used to specify the registers take the form register\_page.bit:bit, register\_page.bit, register.bit:bit, or register.bit.

For example:

Register 16 page 2 bits 5 to 2 is specified as 16\_2.5:2.

Register 16 page 2 bits 5 is specified as 16\_2.5.

It takes four MDIO write commands to write the same register to the same value on all 8 ports. Register 22.15:14 can be used to selectively ignore PHYAD[4:2] and PHYAD[1:0] as shown in Table 31 so that the same register address can be written to all four ports in one MDIO write command. PHYAD[4:0] will still be decoded for read commands.

Care must be taken to setup multiple port write. To enable the concurrent write access write register 22 four times in a row with bit 14 set to 1 – once to each PHYAD[4:0]. The values written on all 16 bits must be the same otherwise unpredictable behavior will occur.

Once the four write commands to register 22 are issued, all subsequent writes will be concurrent to all ports including writes to register 22.

Concurrent write access will continue as long as every write to register 22 sets 22.14 to 1.

To disable concurrent write access simply write register 22.14 to 0.

| Register | Function                                             | Setting                                                                                       | Mode | HW<br>Rst | SW<br>Rst |

|----------|------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|-----------|-----------|

| 22.15    | lgnore<br>PHYAD[4:2]                                 | 0 = Use PHYAD[4:2] to decode write commands<br>1 = Ignore PHYAD[4:2] to decode write commands | R/W  | 0         | Retain    |

| 22.14    | lgnore<br>PHYAD[1:0]                                 | 0 = Use PHYAD[1:0] to decode write commands<br>1 = Ignore PHYAD[1:0] to decode write commands | R/W  | 0         | Retain    |

| 22.13:8  | Reserved                                             | 0000000                                                                                       | RO   | 0         | 0         |

| 22.7:0   | Page select<br>for registers<br>0 to 21, 23<br>to 31 | Page Number                                                                                   | R/W  | 00        | Retain    |

### 2.3.2.3 Clause 45 MDC/MDIO Management Interface (XMDIO)

Clause 45 provides extension of Clause 22 MDC/MDIO management interface to access more device registers while retaining its logical compatibility of the frame format. Clause 22 uses frame format with "Start of Frame" code of '01' while Clause 45 uses frame format with "Start of Frame" code of '00'. The extensions for Clause 45 MDIO indirect register accesses are specified in Table 32.

| Frame             | 32-bit<br>Preamble | Start of<br>Frame | Opcode | 5-bit PHY<br>Address<br>(MSB) |       | 2-bit<br>Turnaround | 16-bit ADRESS/DATA<br>Field | Idle |

|-------------------|--------------------|-------------------|--------|-------------------------------|-------|---------------------|-----------------------------|------|

| Address           | 11                 | 00                | 00     | PPPPP                         | DDDDD | 10                  | АААААААААААААА              | z    |

| Write             | 11                 | 00                | 01     | PPPPP                         | DDDDD | 10                  | DDDDDDDDDDDDDDDD            | z    |

| Read              | 11                 | 00                | 11     | PPPPP                         | DDDDD | Z0                  | DDDDDDDDDDDDDDDD            | z    |

| Read<br>Increment | 11                 | 00                | 10     | РРРРР                         | DDDDD | Z0                  | DDDDDDDDDDDDDDD             | Z    |

| Table 32: Exte | ensions for Manac | gement Frame Forn | nat for Indirect Access |

|----------------|-------------------|-------------------|-------------------------|

|----------------|-------------------|-------------------|-------------------------|

Clause 45 MDIO implements a 16-bit address register that stores the address of the register to be accessed. For an address cycle, it contains the address of the register to be accessed on the next cycle. For read, write, post-read increment-address cycles, the field contains the data for the register. At power up and reset, the contents of the register are undefined. Write, read, and post-read-increment-address frames access the address register, though write and read frames do not modify the contents of the address register.

#### 2.3.2.4 Clause 22 Access to Clause 45 MDIO Manageable Device (MMD)

Clause 22 provides access to registers in a clause 45 MDIO MMD space using Register 13 and 14. Register 22.7:0 must be set to 0 to 7. If Register 22:7:0 is 8 to 255, the MMD registers are not accessible.

The MMD Access Control Register and Address/Data Register definitions are shown in Table 33 and Table 34.

| Table 33: | MMD Access Control Register |

|-----------|-----------------------------|

|           | Page 0, Register 13         |

| Bits  | Field    | Mode | HW Rst | SW Rst | Description                                                                                                                                                                                    |

|-------|----------|------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:14 | Function | R/W  | 0x0    | 0x0    | <ul> <li>15:14</li> <li>00 = Address</li> <li>01 = Data, no post increment</li> <li>10 = Data, post increment on reads and writes</li> <li>11 = Data, post increment on writes only</li> </ul> |

| 13:5  | Reserved | RO   | 0x000  | 0x000  | Reserved                                                                                                                                                                                       |

| 4:0   | DEVAD    | RO   | 0x00   | 0x00   | Device address                                                                                                                                                                                 |

#### Table 34: MMD Access Address/Data Register Page 0, Register 14

| Bits | Field        | Mode | HW Rst | SW Rst | Description                                                                                                                                      |

|------|--------------|------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | Address Data | R/W  | 0x0000 | 0x0000 | If 13.15:14 = 00, MMD DEVAD's address register.<br>Otherwise, MMD DEVAD's data register as indicated by<br>the contents of its address register. |

#### Write Operation

To write to the MMD register access:

- 1. To Register 13, write the Function field to 00 (address) and DEVAD field with the device address value;

- 2. To Register 14, write the MMD's register address value;

- 3. To Register 13, write the Function field to 01 (Data, no post increment) and DEVAD field to the same device address value (as step #1);

- 4. To Register 14, write the content to be written to the selected MMD's register

Step 1 and 2 can be skipped if the MMD's address register was previously configured.

#### **Read Operation**

To read from the MMD register access:

- 1. To Register 13, write the Function field to 00 (address) and DEVAD field with the device address value;

- 2. To Register 14, write the MMD's register address value;

- 3. To Register 13, write the Function field to 01 (Data, no post increment) and DEVAD field to the same device address value (as step #1);

- 4. From Register 14, read the content from the selected MMD's register.

Step 1 and 2 can be skipped if the MMD's address register was previously configured.

#### Write/Read Operation with Post Increment Function

Function '10' can be used to increment the address after each read and write access. Function '11' can be used to increment the address after write operation only. Function '11' enables a read-modify-write capability for successive addressed registers within the MMD.

# 2.4 Power Supplies

The device requires three power supplies: 1.05V, 1.5V, and 3.3V. Additional power supplies may be required if 1.8V/2.5V is used for VDDOR/VDDOL.

Once the voltage is selected for the VDDO, the I/Os are not compatible with other voltage.

# 2.4.1 AVDD33

AVDD33 is used as 3.3V analog supply.

## 2.4.2 AVDD15

AVDD15 is the 1.5V supply. AVDD15 is used as the analog supply REF\_CLKP, REF\_CLKN, and PTP\_CLKP/PTP\_CLKN. AVDD15 is also used as USGMII SERDES, RESET, TSTPT and HSDACP/HSDACN supplies.

## 2.4.3 DVDD

DVDD is used for the digital logic. DVDD is the 1.15V digital supply.

## 2.4.4 VDDOL

VDDOL supplies the digital I/O pins for TDO, TDI, TMS, TCK, TRST, RCLK, LED, CONFIG, and CLK\_SEL[1:0].

VDDOL requires 2.5V or 3.3V.

## 2.4.5 VDDOR

VDDOR supplies the digital I/O pins for PTP\_TRIG\_IN, RESET, MDC/MDIO, and INTn. VDDOR requires 1.8V, 2.5V, or 3.3V. The voltage selection is done at the deassertion of hardware reset. Once set, the I/O is not tolerant to other I/O voltage levels.

## 2.4.6 Power Supply Sequencing

On power-up, no special power supply sequencing is required.

# **3** Electrical Specifications

# 3.1 Absolute Maximum Ratings<sup>1</sup>

#### Table 35: Absolute Maximum Ratings

Stresses above those listed in Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

| Symbol               | Parameter                                          | Min  | Тур | Max               | Units |

|----------------------|----------------------------------------------------|------|-----|-------------------|-------|

| V <sub>DDA15</sub>   | Power Supply Voltage on AVDD15 with respect to VSS | -0.5 |     | 1.65              | V     |

| $V_{DD}$             | Power Supply Voltage on DVDD with respect to VSS   | -0.5 |     | 1.5               | V     |

| V <sub>DDA33</sub>   | Power Supply Voltage on AVDD33 with respect to VSS | -0.5 |     | 3.63              | V     |

| V <sub>DDOL</sub>    | Power Supply Voltage on VDDOL with respect to VSS  | -0.5 |     | VDDOL<br>+10%     | V     |

| V <sub>DDOR</sub>    | Power Supply Voltage on VDDOR with respect to VSS  | -0.5 |     | VDDOR +<br>10%    | V     |

| V <sub>PIN</sub>     | Voltage applied to any digital input pin           | -0.5 |     | VDDO +<br>0.7V    | V     |

| T <sub>STORAGE</sub> | Storage temperature                                | -55  |     | +125 <sup>1</sup> | °C    |

1. 125 °C is only used as bake temperature for not more than 24 hours. Long term storage (e.g weeks or longer) should be kept at 85 °C or lower.

<sup>1.</sup> On power-up, no special power supply sequencing is required.

#### **Recommended Operating Conditions** 3.2

#### Table 36: Recommended Operating Conditions

| Symbol Desemptor Condition Min Type May Units |                                          |                                       |      |                           |                  |       |  |  |  |

|-----------------------------------------------|------------------------------------------|---------------------------------------|------|---------------------------|------------------|-------|--|--|--|

| Symbol                                        | Parameter                                | Condition                             | Min  | Тур                       | Max              | Units |  |  |  |

| V <sub>DDA15</sub> <sup>1</sup>               | AVDD15 supply                            | For AVDD = 1.5V                       | 1.42 | 1.50                      | 1.58             | V     |  |  |  |

| V <sub>DDA33</sub>                            | AVDD33 supply                            | For AVDD33                            | 3.13 | 3.3                       | 3.47             | V     |  |  |  |

| $V_{DD}^{1}$                                  | DVDD supply                              | For DVDD at 1.15V                     | 1.11 | 1.15                      | 1.18             | V     |  |  |  |

| V <sub>DDOL</sub> <sup>1</sup>                | VDDOL supply                             | For VDDOL at 2.5V                     | 2.38 | 2.5                       | 2.63             | V     |  |  |  |

|                                               |                                          | For VDDOL at 3.3V                     | 3.13 | 3.3                       | 3.47             | V     |  |  |  |

| V <sub>DDOR</sub> <sup>1</sup>                | VDDOR supply                             | For VDDOR at 1.8V                     | 1.71 | 1.8                       | 1.89             | V     |  |  |  |

|                                               |                                          | For VDDOR at 2.5V                     | 2.38 | 2.5                       | 2.63             | V     |  |  |  |

|                                               |                                          | For VDDOR at 3.3V                     | 3.13 | 3.3                       | 3.47             | V     |  |  |  |

| RSET                                          | Internal bias reference                  | Resistor connected to V <sub>SS</sub> |      | 5000 ±<br>1%<br>Tolerance |                  | Ω     |  |  |  |

| T <sub>A</sub>                                | Commercial Ambient operating temperature |                                       | 0    |                           | 70 <sup>2</sup>  | °C    |  |  |  |

| TJ                                            | Maximum junction<br>temperature          |                                       |      |                           | 125 <sup>3</sup> | °C    |  |  |  |

1. Maximum noise allowed on supplies is 50 mV peak-peak.

Commercial operating temperatures are typically below 70 °C, e.g, 45 °C ~55 °C. The 70 °C max is Marvell<sup>®</sup> specification limit

Refer to white paper on TJ Thermal Calculations for more information.

# 3.3 Package Thermal Information

# 3.3.1 Thermal Conditions for 128-pin, LQFP Package

Table 37: Thermal Conditions for 128-pin, LQFP Package

| Symbol          | Parameter                                                                                                                                                                                | Condition                                                         | Min | Тур  | Max | Units |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|------|-----|-------|

| $\theta_{JA}$   | Thermal resistance <sup>1</sup> - junction to ambient for the                                                                                                                            | JEDEC 3 in. x 4.5 in.<br>4-layer PCB with no air flow             |     | 22   |     | °C/W  |

|                 | 128-Pin, LQFP package                                                                                                                                                                    | JEDEC 3 in. x 4.5 in.<br>4-layer PCB with 1<br>meter/sec air flow |     | 16.5 |     | °C/W  |

|                 | $\theta_{JA} = (T_J - T_A)/P$<br>P = Total power dissipation                                                                                                                             | JEDEC 3 in. x 4.5 in.<br>4-layer PCB with 2<br>meter/sec air flow |     | 15.5 |     | °C/W  |

|                 |                                                                                                                                                                                          | JEDEC 3 in. x 4.5 in.<br>4-layer PCB with 3<br>meter/sec air flow |     | 15   |     | °C/W  |

| ΨJT             | Thermal characteristic parameter <sup>a</sup> - junction to top                                                                                                                          | JEDEC 3 in. x 4.5 in.<br>4-layer PCB with no air flow             |     | 0.6  |     | °C/W  |

|                 | center of the 128-Pin, LQFP<br>package                                                                                                                                                   | JEDEC 3 in. x 4.5 in.<br>4-layer PCB with 1<br>meter/sec air flow |     | 0.69 |     | °C/W  |

|                 | $\begin{array}{l} \psi_{JT} = (T_{J}\text{-}T_{top})/P. \\ P = \text{ Total power dissipation,} \\ T_{top:} \text{ Temperature on the top} \\ \text{center of the package.} \end{array}$ | JEDEC 3 in. x 4.5 in.<br>4-layer PCB with 2<br>meter/sec air flow |     | 0.75 |     | °C/W  |

|                 |                                                                                                                                                                                          | JEDEC 3 in. x 4.5 in.<br>4-layer PCB with 3<br>meter/sec air flow |     | 0.9  |     | °C/W  |

| θ <sub>JC</sub> | Thermal resistance <sup>a</sup> -<br>junction to case for the<br>128-Pin, LQFP package                                                                                                   | JEDEC with no air flow                                            |     | 15.5 |     | °C/W  |

|                 | $\theta_{JC} = (T_{J}, T_C)/P_{top}$<br>$P_{top} = Power dissipation$<br>from the top of the package                                                                                     |                                                                   |     |      |     |       |

| $\theta_{JB}$   | Thermal resistance <sup>a</sup> -<br>junction to board for the<br>128-Pin, LQFP package                                                                                                  | JEDEC with no air flow                                            |     | 8    |     | °C/W  |

|                 | $\theta_{JB} = (T_J - T_B)/P_{bottom}$<br>$P_{bottom} = Power dissipation$<br>from the bottom of the<br>package to the PCB surface.                                                      |                                                                   |     |      |     |       |

1. Refer to white paper on TJ Thermal Calculations for more information.

#### **Current Consumption** 3.4

Use current specifications for 88E1680 3.4.1

# 3.5 Digital I/O DC Operating Conditions

# 3.5.1 Digital Pins

#### Table 38: Digital Pins

(Over full range of values listed in the Recommended Operating Conditions unless otherwise specified)

| Symbol           | Parameter                       | Pins                              | Condition   | Min            | Тур | Max            | Units |

|------------------|---------------------------------|-----------------------------------|-------------|----------------|-----|----------------|-------|

| VIH              | Input high<br>voltage           | All digital inputs                | VDDO = 3.3V | 2.0            |     | VDDO +<br>0.6V | V     |

|                  |                                 |                                   | VDDO = 2.5V | 1.75           |     | VDDO +<br>0.6V | V     |

|                  |                                 |                                   | VDDO = 1.8V | 1.26           |     | VDDO +<br>0.6V | V     |

| VIL              | Input low                       | All digital inputs                | VDDO = 3.3V | -0.3           |     | 0.8            | V     |

|                  | voltage                         | bitage                            | VDDO = 2.5V | -0.3           |     | 0.75           | V     |

|                  |                                 |                                   | VDDO = 1.8V | -0.3           |     | 0.54           | V     |

| VOH              | High level<br>output<br>voltage | All digital outputs               | IOH = -4 mA | VDDO<br>- 0.4V |     |                | V     |

| VOL              | Low level<br>output<br>voltage  | All digital outputs               | IOL = 4 mA  |                |     | 0.4            | V     |

| I <sub>ILK</sub> | Input leakage current           | With internal<br>pull-up resistor |             |                |     | 10<br>-50      | uA    |

|                  |                                 | All others<br>without resistor    |             |                |     | 10             | uA    |

| CIN              | Input<br>capacitance            | All pins                          |             |                |     | 5              | pF    |

## 3.5.2 LED Pins - Single LED Mode (Reg 1\_28.10 = 0)

#### Table 39: LED Pins - Single LED Mode (Reg 1\_28.10 = 0)

(Over full range of values listed in the Recommended Operating Conditions unless otherwise specified)

| Symbol           | Parameter                              | Pins            | Condition    | Min            | Тур | Max       | Units |

|------------------|----------------------------------------|-----------------|--------------|----------------|-----|-----------|-------|

| VOH              | High level<br>output<br>voltage        | All LED outputs | IOH = -10 mA | VDDO<br>- 0.4V |     |           | V     |

| VOL              | Low level<br>output<br>voltage         | All LED outputs | IOL = 10 mA  |                |     | 0.4       | V     |

| I <sub>MAX</sub> | Total<br>maximum<br>current per<br>LED | All LED pins    |              |                |     | 12.5      | mA    |

| I <sub>ILK</sub> | Input leakage<br>current               | All LED pins    |              |                |     | 10<br>-50 | uA    |

| CIN              | Input<br>capacitance                   | All LED pins    |              |                |     | 5         | pF    |

## 3.5.3 LED Pins - Matrix LED Mode (Reg 1\_28.10 = 1)

#### Table 40: LED Pins - Matrix LED Mode (Reg 1\_28.10 = 1)

(Over full range of values listed in the Recommended Operating Conditions unless otherwise specified)

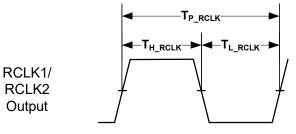

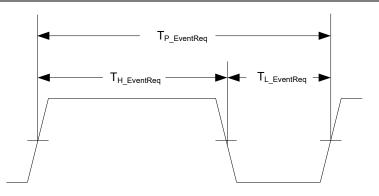

| Symbol               | Parameter                                  | Pins            | Condition     | Min            | Тур | Max       | Units |